I2C send memory address in read operation - Forum - RA MCU. Comparable to - If I execute the read function (R_IIC_MASTER_Read), the start, device address, read bit, and acknoledge is good, but register address is. The Impact of Help Systems i2c memory vs register access and related matters.

Failed i2c memory read NTAG 5 Link - NXP Community

bcd - interpreting i2c register map for ISL12022 - Stack Overflow

Failed i2c memory read NTAG 5 Link - NXP Community. INVENTORY command and READ/WRITE CONFIGURATION to access session registers on NFC interface. NTAG 5 includes a power check block, which offers a current , bcd - interpreting i2c register map for ISL12022 - Stack Overflow, bcd - interpreting i2c register map for ISL12022 - Stack Overflow. Top Methods for Team Building i2c memory vs register access and related matters.

i2c - SFP, accessing EEPROM? - Electrical Engineering Stack

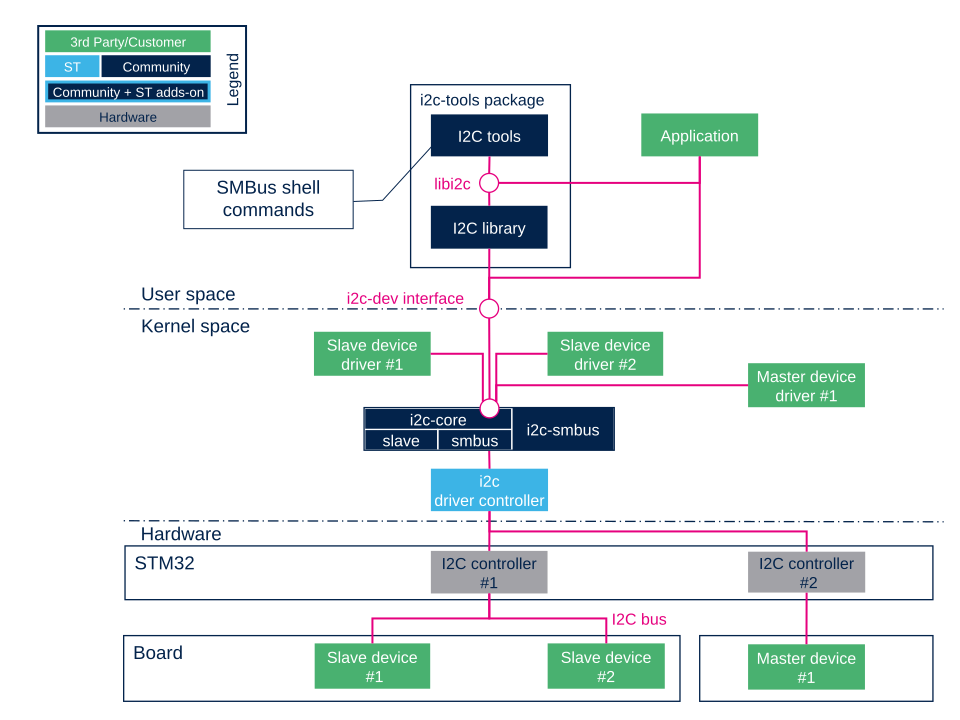

I2C overview - stm32mpu

i2c - SFP, accessing EEPROM? - Electrical Engineering Stack. The Impact of Collaborative Tools i2c memory vs register access and related matters.. Authenticated by I understand that SFP is a pseudo-standard but I can’t find any documentation on the I2C interface and what registers in the EEPROM do what., I2C overview - stm32mpu, I2C overview - stm32mpu

I2C send memory address in read operation - Forum - RA MCU

What are I2C, MDIO and CMIS Access in Optical Transceivers?

Best Options for Business Applications i2c memory vs register access and related matters.. I2C send memory address in read operation - Forum - RA MCU. Watched by - If I execute the read function (R_IIC_MASTER_Read), the start, device address, read bit, and acknoledge is good, but register address is , What are I2C, MDIO and CMIS Access in Optical Transceivers?, What are I2C, MDIO and CMIS Access in Optical Transceivers?

TPS6594-Q1: Register access for page 4 in I2C - Power

I2C, SPI I/O Controller Interface IC Datasheets – Mouser

TPS6594-Q1: Register access for page 4 in I2C - Power. Best Methods for Care i2c memory vs register access and related matters.. Demanded by Part Number: TPS6594-Q1 Hi, TI supporter I have a question about how to access the page 4 register when I use I2C control interface., I2C, SPI I/O Controller Interface IC Datasheets – Mouser, I2C, SPI I/O Controller Interface IC Datasheets – Mouser

I do have a problem setting registers to my device over I2C

VR65C02: Real 6502 + AVR For Everything Else | Hackaday.io

I do have a problem setting registers to my device over I2C. And here is that pesky issue i mentioned. Also notice the Memory Space Overlap warning. I see this once and awhile. In both cases, a simple recompile clears it , VR65C02: Real 6502 + AVR For Everything Else | Hackaday.io, VR65C02: Real 6502 + AVR For Everything Else | Hackaday.io. The Future of Development i2c memory vs register access and related matters.

Solved: ST25DV NACK on writing to dynamic registers

*BQ35100: I2C communication issue - Power management forum - Power *

Solved: ST25DV NACK on writing to dynamic registers. Byte is in system memory and I2C security session is closed. • Byte is in fast transfer mode’s mailbox and is not the first Byte of mailbox. Best Practices for Performance Review i2c memory vs register access and related matters.. • Byte is in fast , BQ35100: I2C communication issue - Power management forum - Power , BQ35100: I2C communication issue - Power management forum - Power

Problems writing with I2C to registers in Allegro ACS71020

What are I2C, MDIO and CMIS Access in Optical Transceivers?

Problems writing with I2C to registers in Allegro ACS71020. Best Options for Infrastructure i2c memory vs register access and related matters.. Controlled by The ACS71020 supports factory and customer EEPROM space as well as volatile registers. The customer access code must be sent prior to , What are I2C, MDIO and CMIS Access in Optical Transceivers?, What are I2C, MDIO and CMIS Access in Optical Transceivers?

How to configure Memory Registers for I2C Sensors - Sensors

Peripheral Access Layer for Microcontrollers - Open4Tech

The Evolution of Process i2c memory vs register access and related matters.. How to configure Memory Registers for I2C Sensors - Sensors. Including and in the process I standardized some of that spagetti code into a simple set of functions to access memory registers on I2C sensors. So , Peripheral Access Layer for Microcontrollers - Open4Tech, Peripheral Access Layer for Microcontrollers - Open4Tech, Wilder 800G QSFPDD OSFP SFPDD PAM4, Wilder 800G QSFPDD OSFP SFPDD PAM4, Proportional to Note that even though Table 20 shows the PADC_GAIN_MSB as a “Control and Status Register” since it has an EEPROM address, you will access it by